#### ATmega128

Lock Bits & Fuse Bits System Clock I/O Ports JTAG

## **Lock Bits**

| Bit No. | Description                     | Default Value                                                         |                                                                                                                                                                                       |

|---------|---------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7       | -                               | 1 (unprogrammed)                                                      |                                                                                                                                                                                       |

| 6       | _                               | 1 (unprogrammed)                                                      |                                                                                                                                                                                       |

| 5       | Boot lock bit                   | 1 (unprogrammed)                                                      | Drotect Dept Londer Costien                                                                                                                                                           |

| 4       | Boot lock bit                   | 1 (unprogrammed)                                                      | Protect Boot Loader Section                                                                                                                                                           |

| 3       | Boot lock bit                   | 1 (unprogrammed)                                                      | Protect Application Section                                                                                                                                                           |

| 2       | Boot lock bit                   | 1 (unprogrammed)                                                      | Protect Application Section                                                                                                                                                           |

| 1       | Lock bit                        | 1 (unprogrammed)                                                      |                                                                                                                                                                                       |

| 0       | Lock bit                        | 1 (unprogrammed)                                                      |                                                                                                                                                                                       |

|         | 7<br>6<br>5<br>4<br>3<br>2<br>1 | 7-6-5Boot lock bit4Boot lock bit3Boot lock bit2Boot lock bit1Lock bit | 7-1 (unprogrammed)6-1 (unprogrammed)5Boot lock bit1 (unprogrammed)4Boot lock bit1 (unprogrammed)3Boot lock bit1 (unprogrammed)2Boot lock bit1 (unprogrammed)1Lock bit1 (unprogrammed) |

#### Table 115. Lock Bit Byte

"1" means unprogrammed, "0'means programmed Note:

#### Table 116. Lock Bit Protection Modes

| Memory Lock Bits |     | ts  | Protection Type                                                                                                                                                                                                           |             |

|------------------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| LB mode          | LB2 | LB1 |                                                                                                                                                                                                                           |             |

| 1                | 1   | 1   | No memory lock features enabled.                                                                                                                                                                                          |             |

| 2                | 1   | 0   | Further programming of the Flash and EEPROM is<br>disabled in Parallel and SPI/JTAG Serial Programming<br>mode. The Fuse bits are locked in both Serial and Parallel<br>Programming mode. <sup>(1)</sup>                  | Write Prote |

| 3                | 0   | 0   | Further programming and verification of the Flash and<br>EEPROM is disabled in Parallel and SPI/JTAG Serial<br>Programming mode. The Fuse bits are locked in both<br>Serial and Parallel Programming mode. <sup>(1)</sup> | Read/Write  |

#### tection

#### e Protection

## **Fuse Bits: Extended Fuse Byte**

Table 117. Extended Fuse Byte

| Extended Fuse Byte   | Bit No. | Description                  | Default Value    |

|----------------------|---------|------------------------------|------------------|

| -                    | 7       | _                            | 1                |

| -                    | 6       | _                            | 1                |

| -                    | 5       | _                            | 1                |

| -                    | 4       | _                            | 1                |

| -                    | 3       | _                            | 1                |

| -                    | 2       | _                            | 1                |

| M103C <sup>(1)</sup> | 1       | ATmega103 compatibility mode | 0 (programmed)   |

| WDTON <sup>(2)</sup> | 0       | Watchdog Timer always on     | 1 (unprogrammed) |

## **Fuse Bits: Fuse High Bytes**

| Fuse High<br>Byte     | Bit No. | Description                                          | Default Value                             |                      |

|-----------------------|---------|------------------------------------------------------|-------------------------------------------|----------------------|

| OCDEN <sup>(4)</sup>  | 7       | Enable OCD                                           | 1 (unprogrammed, OCD<br>disabled)         | OCDR Register Access |

| JTAGEN <sup>(5)</sup> | 6       | Enable JTAG                                          | 0 (programmed, JTAG enabled)              |                      |

| SPIEN <sup>(1)</sup>  | 5       | Enable Serial Program and<br>Data Downloading        | 0 (programmed, SPI prog.<br>enabled)      |                      |

| CKOPT <sup>(2)</sup>  | 4       | Oscillator options                                   | 1 (unprogrammed)                          | Amplitude Adjust.    |

| EESAVE                | 3       | EEPROM memory is preserved<br>through the Chip Erase | 1 (unprogrammed, EEPROM not<br>preserved) |                      |

| BOOTSZ1               | 2       | Select Boot Size (see Table 112 for details)         | 0 (programmed) <sup>(3)</sup>             |                      |

| BOOTSZ0               | 1       | Select Boot Size (see Table 112 for details)         | 0 (programmed) <sup>(3)</sup>             |                      |

| BOOTRST               | 0       | Select Reset Vector                                  | 1 (unprogrammed)                          |                      |

## **Fuse Bits: Fuse Low Byte**

| Fuse Low<br>Byte | Bit No. | Description                      | Default Value                   |

|------------------|---------|----------------------------------|---------------------------------|

| BODLEVEL         | 7       | Brown out detector trigger level | 1 (unprogrammed)                |

| BODEN            | 6       | Brown out detector enable        | 1 (unprogrammed, BOD disabled)  |

| SUT1             | 5       | Select start-up time             | 1 (unprogrammed) <sup>(1)</sup> |

| SUT0             | 4       | Select start-up time             | 0 (programmed) <sup>(1)</sup>   |

| CKSEL3           | 3       | Select Clock source              | 0 (programmed) <sup>(2)</sup>   |

| CKSEL2           | 2       | Select Clock source              | 0 (programmed) <sup>(2)</sup>   |

| CKSEL1           | 1       | Select Clock source              | 0 (programmed) <sup>(2)</sup>   |

| CKSEL0           | 0       | Select Clock source              | 1 (unprogrammed) <sup>(2)</sup> |

Power Level Detector 1: 2.7/ o:4.0/ Start Up time

**Clock Source Selection**

#### **Fuse Bits**

#### Clock Point 1 - CKOPT

The CKOPT fuse selects between two different Oscillator Amplifier modes

# PonyProg2000(obsolete)

#### PonyProg 2000 Setting

| Configuration and Security bits                                             | Configuration and Security bits                                             |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|

|                                                                             |                                                                             |

| □ 7 □ 6 □ BootLock12 □ BootLock11 □ BootLock02 □ BootLock01 □ Lock2 □ Lock1 | □ 7 □ 6 □ BootLock12 □ BootLock11 □ BootLock02 □ BootLock01 □ Lock2 □ Lock1 |

| □ 7 □ 6 □ 5 □ 4 □ 3 □ 2 ₩ M103C □ WDTON                                     |                                                                             |

| CODEN V JTAGEN V SPIEN CKOPT CESAVE V BOOTSZ1 V BOOTSZ0 BOOTRST             | CODEN T JTAGEN T SPIEN T CKOPT T EESAVE T BOOTSZ1 T BOOTSZO BOOTRST         |

| □ BODLEVEL □ BODEN □ SUT1 □ SUT0 □ CKSEL3 □ CKSEL2 □ CKSEL1 □ CKSEL0        | F BODLEVEL F BODEN F SUT1 F SUTO F CKSEL3 F CKSEL2 F CKSEL F CKSEL0         |

|                                                                             |                                                                             |

| Checked items means programmed (bit = 0)                                    | Checked items means programmed (bit = 0)                                    |

| Refer to device datasheet, please                                           | Refer to device datasheet, please                                           |

| Clear All Set All Write Read                                                | Cancel Clear All Set All Write Read                                         |

**Default Status**

#### **Atmel Studio**

| ð     | Start Pa | age - At | tmelStudio |       |     |              |         |              |   |

|-------|----------|----------|------------|-------|-----|--------------|---------|--------------|---|

| File  | Edit     | View     | VAssistX   | Debug | Too | s Window     | Help    |              |   |

| 6     | - 0      | 約 -      | 'a + 놀 🔛   | ¥ 🖌   | >   | Command Pr   | ompt    |              | þ |

|       | ř 🔳      | → 1      | 6          | ÷ ?   | 1   | Device Pack  | Manager |              |   |

| Start | Page ⊰   | ×        |            |       | sta | Device Progr | amming  | Ctrl+Shift+P |   |

| Start | ruge     |          | a          |       | 2   | Add target   |         |              |   |

| JTAGICE mkII (00B00002822) - Device Programming ? |                                   |                                   |                            |               |       |  |  |

|---------------------------------------------------|-----------------------------------|-----------------------------------|----------------------------|---------------|-------|--|--|

| Tool Device<br>JTAGICE mkII Y ATmega              | Interface<br>I128 TITAG CAPPLY    |                                   | rget Voltage<br>4.9 V Read | ¢             |       |  |  |

| Interface settings                                | Use external reset                |                                   |                            |               |       |  |  |

| Tool information                                  | Use external reset                |                                   |                            |               |       |  |  |

| Device information                                | JTAG Daisy chain settings         |                                   |                            |               |       |  |  |

| Oscillator calibration                            | Target device is part of a JTA    | G daisy chain                     |                            |               |       |  |  |

| Memories                                          | List all chained devices below. T | he first line represents the devi | ce with TDO con            | nected to the | e too |  |  |

| Fuses                                             | Description                       | IR Length                         |                            |               |       |  |  |

| Lock bits                                         |                                   |                                   |                            |               |       |  |  |

| Production file                                   | Detect Devices Now                |                                   |                            |               |       |  |  |

|                                                   |                                   |                                   |                            | S             | et    |  |  |

#### **Fuses**

| JTAGICE mkll (00B00000282                                                                                                            | 2) - Device Programming                                         | ? ×                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------|

| Tool Device<br>JTAGICE mkll v ATmeg                                                                                                  | Interface<br>JTAG Y                                             | Device signature     Target Voltage       Apply     0x1E9702     Read     4.9 V     Read |

| Interface settings                                                                                                                   | Fuse Name                                                       | Value                                                                                    |

| Tool information                                                                                                                     |                                                                 |                                                                                          |

| Device information                                                                                                                   | HIGH.SPIEN HIGH.EESAVE                                          |                                                                                          |

| Oscillator calibration                                                                                                               | WHIGH.BOOTSZ                                                    | Boot Flash size=4096 words start address=\$F000 ~                                        |

| Memories                                                                                                                             | HIGH.BOOTRST                                                    | boot riasit size=4090 words start address=3r000                                          |

| Fuses                                                                                                                                | WHIGH.CKOPT                                                     |                                                                                          |

| Lock bits                                                                                                                            | <b>V</b> LOW.BODLEVEL                                           | Brown-out detection level at VCC=4.0 V ×                                                 |

| Production file                                                                                                                      | <b>V</b> LOW.BODEN                                              |                                                                                          |

|                                                                                                                                      | ✓ LOW.SUT_CKSEL                                                 | Ext. Crystal/Resonator High Freq.; Start-up time: 16K CK + 64 ms 🗡                       |

|                                                                                                                                      |                                                                 |                                                                                          |

|                                                                                                                                      | Fuse Register Value                                             |                                                                                          |

|                                                                                                                                      | EXTENDED 0xFF<br>HIGH 0x81                                      |                                                                                          |

|                                                                                                                                      | LOW 0x3F                                                        |                                                                                          |

|                                                                                                                                      | <ul> <li>✓ Auto read</li> <li>✓ Verify after program</li> </ul> | Copy to clipboard<br>ming Program Verify Read                                            |

| Starting operation read regis<br>Reading register EXTENDED.<br>Reading register HIGHOK<br>Reading register LOWOK<br>Read registersOK |                                                                 |                                                                                          |

| <ul> <li>Read registersOK</li> </ul>                                                                                                 |                                                                 |                                                                                          |

#### Lock bits

| JTAGICE mkll (00B00000282                                                                                                                                                  | 2) - Device Programn                                   | ning          |                                                                                      | _              |          | ?        | $\times$ |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------|--------------------------------------------------------------------------------------|----------------|----------|----------|----------|

| Tool Device<br>JTAGICE mkll ~ ATmega                                                                                                                                       | Interfa<br>a128 • JTAG                                 |               | Device signature 0x1E9702 Read                                                       | Target Voltage | <b>*</b> |          |          |

| Interface settings<br>Tool information<br>Device information<br>Oscillator calibration<br>Memories<br>Fuses                                                                | Lock Bit<br>LOCKBIT.LB<br>LOCKBIT.BLB0<br>LOCKBIT.BLB1 | No lock on SF | Value<br>ock features enabled<br>PM and LPM in Applicatio<br>PM and LPM in Boot Sect |                |          |          |          |

| Lock bits<br>Production file                                                                                                                                               | LOCKBIT                                                | Value<br>IxFF |                                                                                      |                |          | to clipb |          |

| Verify after programming<br>To clear lockbits, use Erase Chip on the Memories page.<br>Starting operation read registers<br>Reading register LOCKBITOK<br>Read registersOK |                                                        |               |                                                                                      |                |          |          |          |

| <ul> <li>Read registersOK</li> </ul>                                                                                                                                       |                                                        |               |                                                                                      |                |          |          |          |

#### **Memories**

| JTAGICE mkll (00B000002822)                                                                                 | - Device Programming                                                                                                                  |                                |                                   | ? ×                             |

|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----------------------------------|---------------------------------|

| Tool Device<br>JTAGICE mkll V ATmega                                                                        | Interface<br>I28 TITAG Y Apply                                                                                                        | Device signature 0x1E9702 Read | Target Voltage     4.9 V     Read |                                 |

| Interface settings<br>Tool information<br>Device information<br>Oscillator calibration<br>Memories<br>Fuses | Device<br>Erase Chip ✓ Erase now<br>Flash (128 KB)<br>✓ Erase device before programm<br>✓ Verify Flash after programmin<br>✓ Advanced |                                | Program Verify                    | <ul><li></li><li>Read</li></ul> |

| Lock bits<br>Production file                                                                                | EEPROM (4 KB)                                                                                                                         | ming                           | Program Verify                    | <ul><li>Read</li></ul>          |

| Starting operation read register<br>Reading register LOCKBITOK<br>Read registersOK                          |                                                                                                                                       |                                |                                   |                                 |

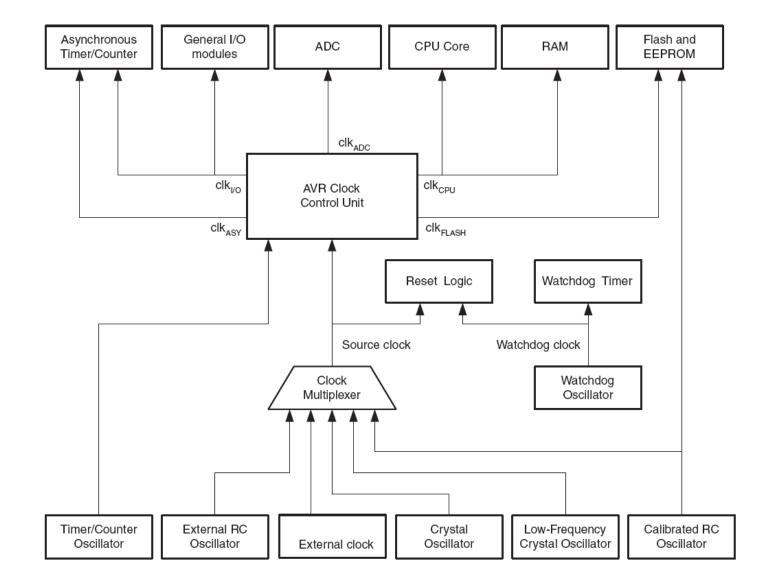

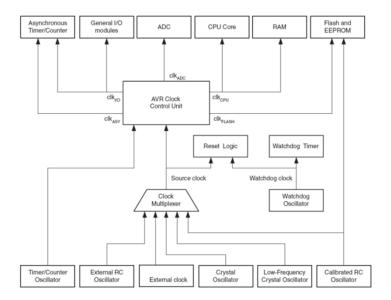

## System Clock

#### CPU Clock – clk<sub>CPU</sub>

- The CPU clock is routed to parts of the system concerned with operation of the AVR core.

- Examples of such modules are the General Purpose Register File, the Status Register and the data memory holding the Stack Pointer.

- Halting the CPU clock inhibits the core from performing general operations and calculations.

#### I/O Clock – clk<sub>I/O</sub>

- The I/O clock is used by the majority of the I/O modules, like Timer/Counters, SPI, and USART.

- The I/O clock is also used by the External Interrupt module, but note that some external interrupts are detected by asynchronous logic, allowing such interrupts to be detected even if the I/O clock is halted. Also note that address recognition in the TWI module is carried out asynchronously when clkI/O is halted, enabling TWI address reception in all sleep modes.

#### Flash Clock – clk<sub>FLASH</sub>

The Flash clock controls operation of the Flash interface. The Flash clock is usually active simultaneously with the CPU clock.

#### Async Timer Clock – clk<sub>ASY</sub>

- Asynchronous Timer clock allows the Asynchronous Timer/Counter to be clocked directly from an external 32 kHz clock crystal.

- The dedicated clock domain allows using this Timer/Counter as a realtime counter even when the device is in sleep mode.

#### ADC Clock – clk<sub>ADC</sub>

- The ADC is provided with a dedicated clock domain. This allows halting the CPU and I/O clocks in order to reduce noise generated by digital circuitry.

- This gives more accurate ADC conversion results.

### **Clock Sources**

| Device Clocking Option             | CKSEL30 <sup>(1)</sup> |

|------------------------------------|------------------------|

| External Crystal/Ceramic Resonator | 1111 - 1010            |

| External Low-frequency Crystal     | 1001                   |

| External RC Oscillator             | 1000 - 0101            |

| Calibrated Internal RC Oscillator  | 0100 - 0001            |

| External Clock                     | 0000                   |

#### **Table 6.** Device Clocking Options Select

Note: 1. For all fuses "1" means unprogrammed while "0" means programmed.

#### **Default Clock Source**

The device is shipped with CKSEL = "0001" and SUT = "10". The default clock source setting is therefore the Internal RC Oscillator with longest startup time. This default setting ensures that all users can make their desired clock source setting using an In-System or Parallel Programmer.

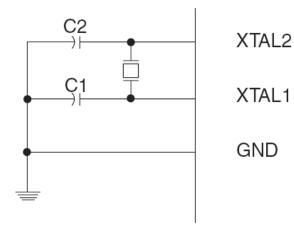

# **Crystal Oscillator**

Table 8. Crystal Oscillator Operating Modes

| •                     | Hz) C1 and C2 for Use with Crystals     |

|-----------------------|-----------------------------------------|

| 01 <sup>(1)</sup> 0.4 | - 0.9 —                                 |

| 0.9                   | - 3.0 12 pF - 22 pF                     |

| 111 3.0               | - 8.0 12 pF - 22 pF                     |

| 110, 111 1            | .0 - 12 pF - 22 pF                      |

|                       | 10         0.9           11         3.0 |

Note: 1. This option should not be used with crystals, only with ceramic resonators.

# **Crystal Oscillator**

| CKSEL0 | SUT10 | Start-up Time from<br>Power-down and<br>Power-save | Additional Delay<br>from Reset (V <sub>CC</sub><br>= 5.0V) | Recommended Usage                          |

|--------|-------|----------------------------------------------------|------------------------------------------------------------|--------------------------------------------|

| 0      | 00    | 258 CK <sup>(1)</sup>                              | 4.1 ms                                                     | Ceramic resonator, fast<br>rising power    |

| 0      | 01    | 258 CK <sup>(1)</sup>                              | 65 ms                                                      | Ceramic resonator, slowly rising power     |

| 0      | 10    | 1K CK <sup>(2)</sup>                               | _                                                          | Ceramic resonator,<br>BOD enabled          |

| 0      | 11    | 1K CK <sup>(2)</sup>                               | 4.1 ms                                                     | Ceramic resonator, fast rising power       |

| 1      | 00    | 1K CK <sup>(2)</sup>                               | 65 ms                                                      | Ceramic resonator, slowly rising power     |

| 1      | 01    | 16K CK                                             | _                                                          | Crystal Oscillator, BOD<br>enabled         |

| 1      | 10    | 16K CK                                             | 4.1 ms                                                     | Crystal Oscillator, fast<br>rising power   |

| 1      | 11    | 16K CK                                             | 65 ms                                                      | Crystal Oscillator,<br>slowly rising power |

#### Table 9. Start-up Times for the Crystal Oscillator Clock Selection

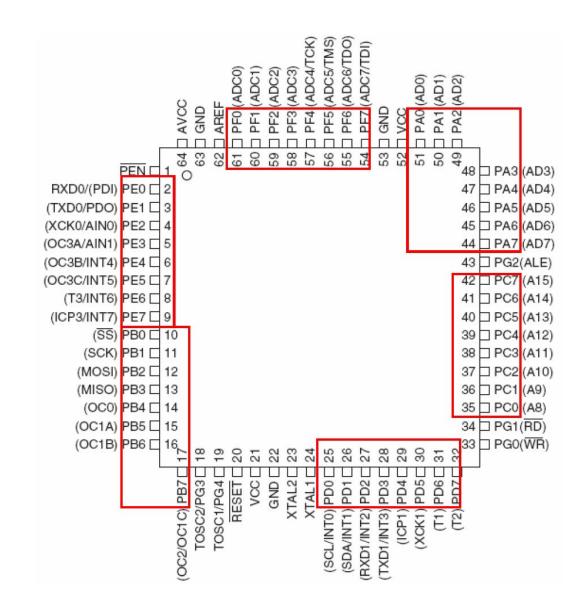

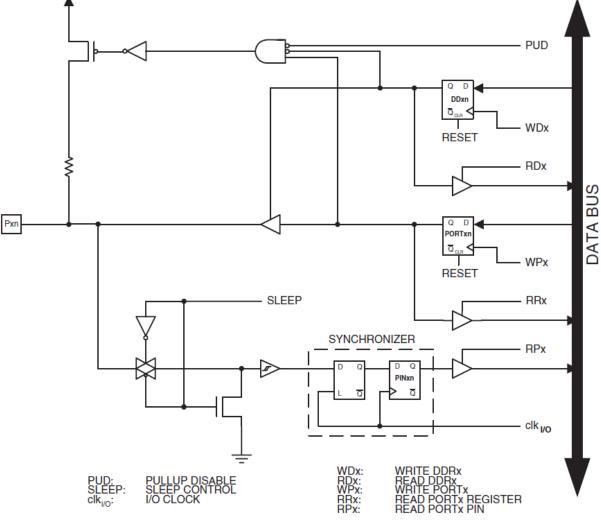

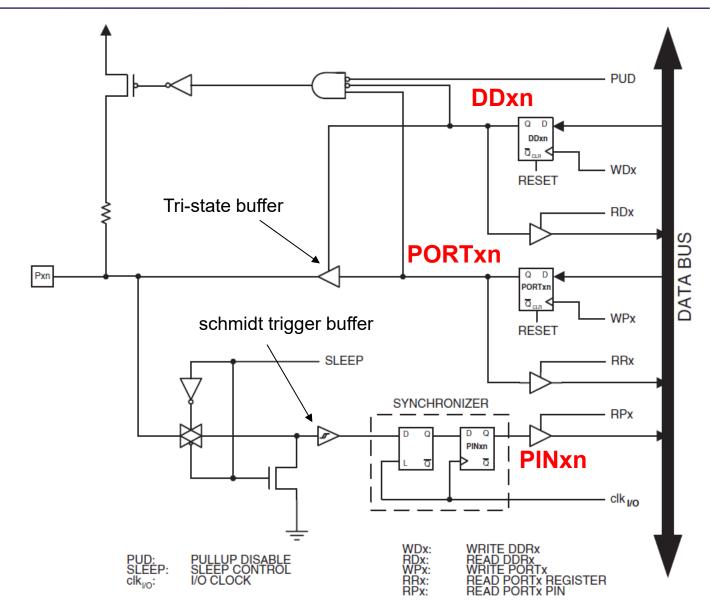

### I/O Ports

# I/O Ports

- Three I/O memory address locations allocated for each port

- Data Register PORTx

- Data Direction Register DDRx

- Port Input Pins PINx

- PINx : read only

- PORTx, DDRx : read/write

- Programmable Pull-up Register

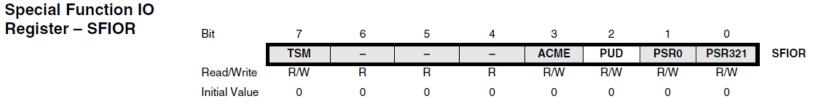

- Pull-up Disable: PUD bit in SFIOR disables the pull-up function for all pins in all ports

# **I/O Port Registers**

#### Example for Port A

| Port A Data Register –<br>PORTA | Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|---------------------------------|---------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|

|                                 |               | PORTA7 | PORTA6 | PORTA5 | PORTA4 | PORTA3 | PORTA2 | PORTA1 | PORTA0 | PORTA |

|                                 | Read/Write    | R/W    |       |

|                                 | Initial Value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

| Port A Data Direction           |               |        |        |        |        |        |        |        |        |       |

| Register – DDRA                 | Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      | _     |

| 5                               |               | DDA7   | DDA6   | DDA5   | DDA4   | DDA3   | DDA2   | DDA1   | DDA0   | DDRA  |

|                                 | Read/Write    | R/W    | •     |

|                                 | Initial Value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

| Port A Input Pins               |               |        |        |        |        |        |        |        |        |       |

| Address – PINA                  | Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      | _     |

|                                 |               | PINA7  | PINA6  | PINA5  | PINA4  | PINA3  | PINA2  | PINA1  | PINA0  | PINA  |

|                                 | Read/Write    | R      | R      | R      | R      | R      | R      | R      | R      | •     |

|                                 | Initial Value | N/A    |       |

|                                 |               |        |        |        |        |        |        |        |        |       |

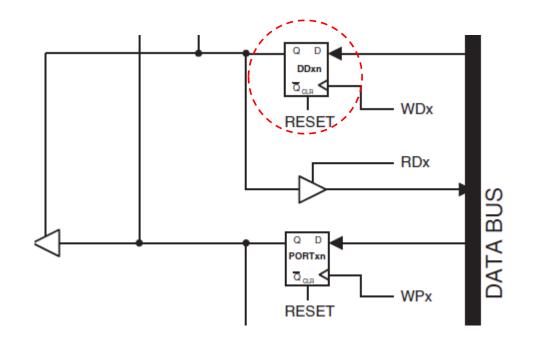

Data Register – PORTx → PORTxn Data Direction Register – DDRx → DDxn Port Input Pins – PINx → PINxn

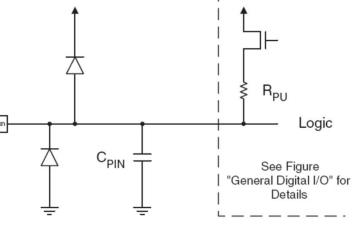

## **ATmega128 Port Architecture**

Port: bi-directional I/O ports with optional internal pull-ups

## **General Digital I/O**

## **Port Pin Configurations**

| DDxn | PORTxn | PUD<br>(in SFIOR) | I/O    | Pull-up | Comment                                     |

|------|--------|-------------------|--------|---------|---------------------------------------------|

| 0    | 0      | Х                 | Input  | No      | Tri-state (Hi-Z)                            |

| 0    | 1      | 0                 | Input  | Yes     | Pxn will source current if ext. pulled low. |

| 0    | 1      | 1                 | Input  | No      | Tri-state (Hi-Z)                            |

| 1    | 0      | Х                 | Output | No      | Output Low (Sink)                           |

| 1    | 1      | Х                 | Output | No      | Output High (Source)                        |

• Bit 2 – PUD: Pull-up disable

Register – SFIOR

When this bit is written to one, the pull-ups in the I/O ports are disabled even if the DDxn and PORTxn Registers are configured to enable the pull-ups ({DDxn, PORTxn} = 0b01). See "Configuring the Pin" on page 67 for more details about this feature.

# **Configuring the Pin - DDxn**

#### DDxn bit in the DDRx Register

- Selects the direction of the pin

- 1: output, 0: input

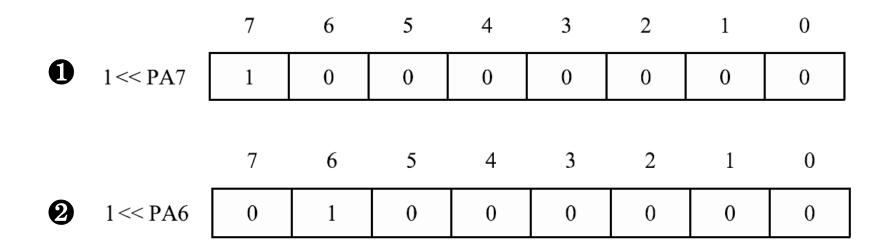

#### **Bitwise Operation Example**

#### #include <avr/io.h>

[B포트의 DDRB, PORTB, PINB 레지스터와 비트명]

| /* DDRB * | /    |   | /* PORTB | */  |   | /* PINB * | /     |   |

|-----------|------|---|----------|-----|---|-----------|-------|---|

| #define   | DDB7 | 7 | #define  | PB7 | 7 | #define   | PINB7 | 7 |

| #define   | DDB6 | 6 | #define  | PB6 | 6 | #define   | PINB6 | 6 |

| #define   | DDB5 | 5 | #define  | PB5 | 5 | #define   | PINB5 | 5 |

| #define   | DDB4 | 4 | #define  | PB4 | 4 | #define   | PINB4 | 4 |

| #define   | DDB3 | 3 | #define  | PB3 | 3 | #define   | PINB3 | 3 |

| #define   | DDB2 | 2 | #define  | PB2 | 2 | #define   | PINB2 | 2 |

| #define   | DDB1 | 1 | #define  | PB1 | 1 | #define   | PINB1 | 1 |

| #define   | DDB0 | 0 | #define  | PB0 | 0 | #define   | PINB0 | 0 |

DDRA = DDRA  $| (1 \langle \langle PA7 \rangle | (1 \langle \langle PA6 \rangle);$

#### **Bitwise Operation Example**

## **Alternate Functions of Port A**

The Port A has an alternate function as the address low byte and data lines for the External Memory Interface.

| Port Pin | Alternate Function                                     |

|----------|--------------------------------------------------------|

| PA7      | AD7 (External memory interface address and data bit 7) |

| PA6      | AD6 (External memory interface address and data bit 6) |

| PA5      | AD5 (External memory interface address and data bit 5) |

| PA4      | AD4 (External memory interface address and data bit 4) |

| PA3      | AD3 (External memory interface address and data bit 3) |

| PA2      | AD2 (External memory interface address and data bit 2) |

| PA1      | AD1 (External memory interface address and data bit 1) |

| PA0      | AD0 (External memory interface address and data bit 0) |

**Table 27.** Port A Pins Alternate Functions

## **Alternate Functions of Port B**

#### **Table 30.** Port B Pins Alternate Functions

| Port Pin | Alternate Functions                                                                                                                 |

|----------|-------------------------------------------------------------------------------------------------------------------------------------|

| PB7      | OC2/OC1C <sup>(1)</sup> (Output Compare and PWM Output for Timer/Counter2 or Output<br>Compare and PWM Output C for Timer/Counter1) |

| PB6      | OC1B (Output Compare and PWM Output B for Timer/Counter1)                                                                           |

| PB5      | OC1A (Output Compare and PWM Output A for Timer/Counter1)                                                                           |

| PB4      | OC0 (Output Compare and PWM Output for Timer/Counter0)                                                                              |

| PB3      | MISO (SPI Bus Master Input/Slave Output)                                                                                            |

| PB2      | MOSI (SPI Bus Master Output/Slave Input)                                                                                            |

| PB1      | SCK (SPI Bus Serial Clock)                                                                                                          |

| PB0      | SS (SPI Slave Select input)                                                                                                         |

#### **Alternate Functions of Port C**

| Table 33. Port C Pins Alternate Functions |

|-------------------------------------------|

|-------------------------------------------|

| Port Pin | Alternate Function |

|----------|--------------------|

| PC7      | A15                |

| PC6      | A14                |

| PC5      | A13                |

| PC4      | A12                |

| PC3      | A11                |

| PC2      | A10                |

| PC1      | A9                 |

| PC0      | A8                 |

## **Alternate Functions of Port D**

#### **Table 36.** Port D Pins Alternate Functions

| Port Pin | Alternate Function                                                         |

|----------|----------------------------------------------------------------------------|

| PD7      | T2 (Timer/Counter2 Clock Input)                                            |

| PD6      | T1 (Timer/Counter1 Clock Input)                                            |

| PD5      | XCK1 <sup>(1)</sup> (USART1 External Clock Input/Output)                   |

| PD4      | ICP1 (Timer/Counter1 Input Capture Pin)                                    |

| PD3      | INT3/TXD1 <sup>(1)</sup> (External Interrupt3 Input or UART1 Transmit Pin) |

| PD2      | INT2/RXD1 <sup>(1)</sup> (External Interrupt2 Input or UART1 Receive Pin)  |

| PD1      | INT1/SDA <sup>(1)</sup> (External Interrupt1 Input or TWI Serial DAta)     |

| PD0      | INT0/SCL <sup>(1)</sup> (External Interrupt0 Input or TWI Serial CLock)    |

## **Alternate Functions of Port E**

| Table 39. | Port E | Pins Alternate | Functions |

|-----------|--------|----------------|-----------|

|-----------|--------|----------------|-----------|

| Port Pin | Alternate Function                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------|

| PE7      | INT7/ICP3 <sup>(1)</sup> (External Interrupt 7 Input or Timer/Counter3 Input Capture Pin)                         |

| PE6      | INT6/ T3 <sup>(1)</sup> (External Interrupt 6 Input or Timer/Counter3 Clock Input)                                |

| PE5      | INT5/OC3C <sup>(1)</sup> (External Interrupt 5 Input or Output Compare and PWM Output C for Timer/Counter3)       |

| PE4      | INT4/OC3B <sup>(1)</sup> (External Interrupt4 Input or Output Compare and PWM Output B for Timer/Counter3)        |

| PE3      | AIN1/OC3A <sup>(1)</sup> (Analog Comparator Negative Input or Output Compare and PWM Output A for Timer/Counter3) |

| PE2      | AIN0/XCK0 <sup>(1)</sup> (Analog Comparator Positive Input or USART0 external clock input/output)                 |

| PE1      | PDO/TXD0 (Programming Data Output or UART0 Transmit Pin)                                                          |

| PE0      | PDI/RXD0 (Programming Data Input or UART0 Receive Pin)                                                            |

### **Alternate Functions of Port F**

| Port Pin | Alternate Function                                      |

|----------|---------------------------------------------------------|

| PF7      | ADC7/TDI (ADC input channel 7 or JTAG Test Data Input)  |

| PF6      | ADC6/TDO (ADC input channel 6 or JTAG Test Data Output) |

| PF5      | ADC5/TMS (ADC input channel 5 or JTAG Test Mode Select) |

| PF4      | ADC4/TCK (ADC input channel 4 or JTAG Test ClocK)       |

| PF3      | ADC3 (ADC input channel 3)                              |

| PF2      | ADC2 (ADC input channel 2)                              |

| PF1      | ADC1 (ADC input channel 1)                              |

| PF0      | ADC0 (ADC input channel 0)                              |

### **Alternate Functions of Port G**

| Table 45. Port G Pins Alternate Function |

|------------------------------------------|

|------------------------------------------|

| Port Pin | Alternate Function                            |

|----------|-----------------------------------------------|

| PG4      | TOSC1 (RTC Oscillator Timer/Counter0)         |

| PG3      | TOSC2 (RTC Oscillator Timer/Counter0)         |

| PG2      | ALE (Address Latch Enable to external memory) |

| PG1      | RD (Read strobe to external memory)           |

| PG0      | WR (Write strobe to external memory)          |

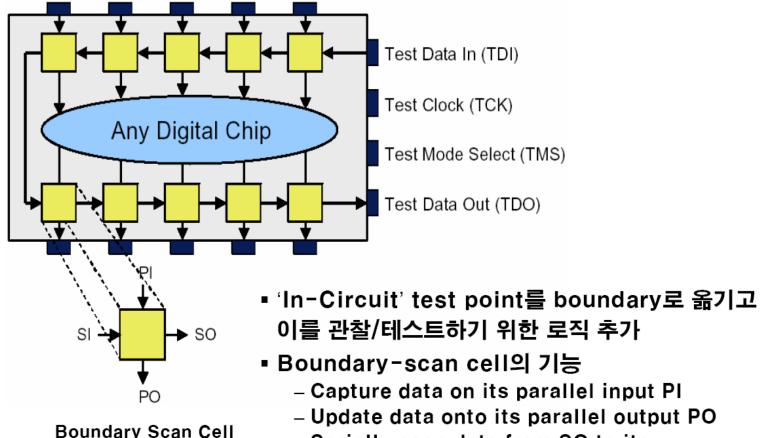

# **JTAG/IEEE1149.1**

#### ▪ 배경

- 초기에는 조립된 PCB(Printed Circuit Board)의 시험을 목적으로 연구

- 기존의 테스트: Bed-of-Nails Probing

- 디바이스 패키징 및 부품 실장 기술 발전

- SMD 출현, 핀의 고집적화(예:BGA)

- ・ 고집적, 표면 실장, 양면 실장, 다층화

- Physical access가 어렵게 되어 기존 방법으로 테스트가 어려움

- Programmable logic device의 on-board programming이 요구됨

#### ▪ 해결책

- 테스트를 위해 표준화된 로직(TAP) 및 테스트 핀 (Boundary Scan Cell)을 칩에 내장

- 테스트 방법 표준화

- Boundary Scan Architecture

- Test Access Port(TAP)

## **JTAG/IEEE1149.1**

- 많은 프로세서 제조업체가 JTAG interface를 확장 및 응용

- On-chip debug feature (e.g. on-chip breakpoints)에 접근 및 제어

- DRAM 등의 메모리 접근 또는 플래시 등의 로직 디바이스 프로그래밍

- JTAG interface는 시리얼 인터페이스를 가지며 기본적으로 다음 5개의 signal로 구성

- nTRST: test reset

- TMS: test mode select

- TDI: test data input

- TDO: test data output

- TCK: test clock

#### ■ 디버그 목적으로 몇 개의 신호를 추가

- nRESET(=nSRST): chip reset

- VTref: 기준 전압 제공

- DBGRQ, DBGACK: 외부 trigger signal을 사용

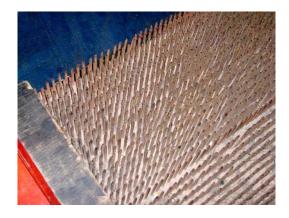

# **JTAG/IEEE1149.1**

- 칩 내부에 본래의 기능을 구현한 Core Logic과 테스트 및 기타 목적을 위한 JTAG 블록이 있다

- JTAG 블록은 TAP Controller와 Register들로 구성되어 있으며 TDI, TDO를 통해 데이터를 주고 받을 수 있 다

- JTAG operation은 TAP controller 에 의해 제어된다

◆ IEEE 1149.1 Device Architecture

# **JTAG: Boundary Scan**

- Serially scan data from SO to its neighbor's SI

- Behave transparently: PI passes to PO